SK하이닉스 “10나노 1c, 원팀 정신으로 개발 성공…HBM 등 여러 D램에 적용”

|

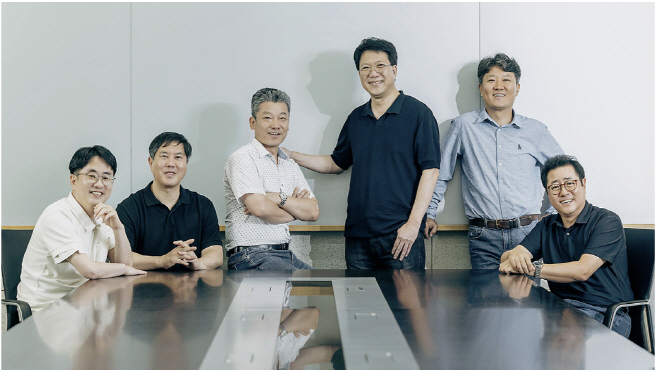

SK하이닉스의 1c 테크 태스크포스(TF)에 속한 오태경 부사장은 10일 자사 뉴스룸 인터뷰에서 "1c 기술 개발을 총괄한 1c Tech TF의 가장 큰 목표는 '1등 개발'이었다"며 "이를 위해 우리는 이미 우수성이 증명된 1b 플랫폼을 확장하는 방식으로 개발하는 전략을 선택했다"고 밝혔다.

그러면서 "테스트, 설계, 양산 준비 등 기존의 3단계 개발 방식을 설계, 양산 준비 등 2단계로 효율화했으며, 커패시터 모듈과 같은 고난도의 기술 요소를 양산 공정에서 바로 개발하는 방식을 택했다"며 "덕분에 전세대 제품 대비 2개월이나 단축해 1c 기술 개발에 성공할 수 있었다"고 말했다.

SK하이닉스는 최근 10나노급 6세대(1c) 미세공정을 적용한 16Gb(기가비트) DDR5 D램을 개발하는 데 성공했다. 연내 1c DDR5의 양산 준비를 마치고 내년부터 시장에 제품을 본격 공급할 계획이다. 이 제품은 고성능 데이터센터에 주로 활용될 예정이다.

1c 기술을 적용한 DDR5의 동작 속도는 8Gbps(초당 기가비트)로 이전 세대인 1b DDR5보다 11% 빨라졌으며, 전력 효율은 9% 이상 개선됐다. 여기에 SK하이닉스는 극자외선(EUV) 공정에 신소재를 개발해 적용하고, 설계 기술 혁신을 통해 공정 효율을 극대화했으며 원가 절감까지 이뤄냈다.

오 부사장은 "무엇보다 구성원들의 원팀 정신이 모든 성과를 견인했다"며 "2단계 개발 방식 도입과 EUV 패터닝 성능 및 원가 개선을 위한 신규 소재 개발 등은 탄탄한 협업 체계가 없었다면 성공할 수 없었을 것"이라고 강조했다.

정창교 D램 PE(프로덕트 엔지니어링) 담당 부사장은 1c 기술에서 주요 성능의 수준을 높이는 트리밍 기술을 활용해 수율과 품질을 확보했다고 설명했다. 트리밍 기술은 반도체 설계 변경 없이 전자식 퓨즈(eFuse)를 활용해 성능을 상향시키는 기술이다. 또 1b 플랫폼을 확장하는 방식으로 개발 시간과 시행착오도 줄였다.

SK하이닉스는 1c를 향후 HBM, LPDDR, GDDR 등 모든 차세대 D램 제품군에 적용할 계획이다. 2026년 개발이 예상되는 7세대 HBM인 HBM4E부터 1c 기술이 적용될 전망이다.

손수용 개발테스트 담당 부사장은 "1c 개발 성공으로 SK하이닉스는 압도적인 기술 경쟁력을 입증했지만 1c DDR5는 시작일 뿐"이라며 "앞으로 1c 기술은 다양한 D램 제품에 적용돼 다양한 고객 니즈에 완벽하게 부응할 것"이라고 말했다.

반도체 업계는 10나노대 D램부터 세대별로 알파벳 기호를 붙여 호칭하고 있다. 1x(1세대), 1y(2세대), 1z(3세대), 1a(4세대), 1b(5세대)에 이어 1c는 6세대 기술이다. 세대를 거듭할수록 기술 난도가 크게 올라 수율 확보, 시간 단축 등에 어려움이 따른다.

많이 본 뉴스

연예가 핫 뉴스

오늘의 주요뉴스

- 트럼프, 두번째 암살 시도에 “바이든·해리스 언사 때문”

- 응급실 뺑뺑이 우려 확산…추석 당일 병의원 1785곳 운영

- 추석 귀경길 정체 심화…부산→서울 8시간 10분

- 무더위에 추석 채소가격 고공행진…과일·축산은 안정세

- 與, 野 19일 본회의 예고에 “추석 민심 거스른 정쟁 준비”

- IAEA “북핵 개발, 유엔 안보리 결의 명백한 위반” 규탄

- 민주, ‘문재인 수사’ 검사도 탄핵 고려…明文 다시 연대

- 머스크 “바이든·해리스 암살 시도 없네” 글 올렸다 삭제

- 추석에도 푹푹 찐다…밤엔 구름 사이로 보름달 ‘빼꼼’

- 서울 아파트 시가총액 3년만에 증가…전년比 35조 ‘껑충’